Université Bordeaux 1 Année 2006

Numéro d'ordre: 3228

#### **THESE**

Présentée et soutenue publiquement le 5 octobre 2006 à

# L'UNIVERSITE DE BORDEAUX I Ecole doctorale de Sciences Physiques et de l'Ingénieur

par

Grégory AVENIER

Pour obtenir le grade de

#### **DOCTEUR**

Spécialité : Electronique

# Développement et étude de transistors bipolaires à hétérojonctions Si/SiGe verticaux sur substrats SOI minces

Après avis de :

M. Peter ASHBURN, Professeur Université de Southampton Rapporteurs

Mme Sylvie RETAILLEAU, Professeur IEF d'Orsay

Devant la commission d'examen formée de :

M. Peter ASHBURN, Professeur Université de Southampton Rapporteurs

Mme Sylvie RETAILLEAU, Professeur IEF d'Orsay

M. Gilbert VINCENT, Professeur Université Grenoble1 Examinateurs

M. Yann DEVAL, Professeur

Mme Cristell MANEUX, M.d.C.

M. Alain CHANTRE, H.D.R

Université Bordeaux 1

Université Bordeaux 1

STMicroelectronics

M. Thomas ZIMMER, Professeur Université Bordeaux 1 Directeur de thèse

Thèse préparée à STMicroelectronics, 850 rue Jean Monnet, F-38926 Crolles Cedex

# Remerciements

Tout d'abord, je remercie Marcel ROCHE, ancien directeur de l'équipe de recherche et développement sur les technologies analogiques/RF de STMicroelectronics à Crolles, et André TOUBOUL, directeur du Laboratoire IXL de Bordeaux, d'avoir initié cette thèse CIFRE au sein du Laboratoire commun ST-IXL. Je tiens, par ailleurs, à exprimer ma reconnaissance à Bernard SAUTREUIL et Olivier NOBLANC, qui ont toujours montré un vif intérêt quant au sujet et au déroulement de cette thèse.

Je tiens à remercier, très sincèrement, tous les membres de mon jury de thèse. La variété des domaines de chacun fut une source d'enrichissement de plus au cours de ces trois ans. Ainsi, je remercie Peter ASHBURN et Sylvie RETAILLEAU d'avoir accepté la charge de rapporteur de cette thèse. J'adresse également mes remerciements à Yann DEVAL pour sa participation au jury de thèse dans son rôle de concepteur. Il a ainsi apporté un œil et un souffle nouveau à nos dispositifs. Finalement, ce fut un plaisir de soutenir devant le jury présidé par Gilbert VINCENT, que je remercie également d'avoir veillé à la rigueur scientifique du manuscrit.

Je remercie très chaleureusement Thomas ZIMMER, qui a été durant (presque) trois ans, un directeur de thèse exemplaire et très compréhensif envers le monde industriel. Je tiens à remercier également Cristell MANEUX, qui a fait beaucoup plus que d'assurer l'intérim de la direction de thèse, durant les mois de rédaction.

Je remercie profondément Alain CHANTRE de la confiance qu'il m'a accordée et de m'avoir entraîné (malgré moi ?) dans l'aventure de la thèse. Je ne regrette rien de ces trois années dirigées et cadencées de main de maître. Je remercie également Pascal CHEVALIER de m'avoir initié aux arcanes des technologies BiCMOS (toujours faire la coupe dans les deux directions !)

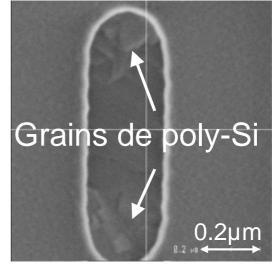

Bien entendu, les technologies les plus performantes ne prennent vie que sur silicium et grâce à toutes les personnes impliquées dans la fabrication de plaquettes. Cette dernière débute par le développement de procédés. Je remercie Cyril, Benoît V., Laurent, Didier

DUTARTRE et les membres (et ex-membres) de son équipe : Alex, Florence D., Benjamin qui ont été, à un moment ou à un autre, indispensables pour leurs épitaxies, leurs polysiliciums, (leur maîtrise incomparable de l'HTF) et leurs implantations. L'équipe de gravure et nettoyage : Fabienne, Thierry, François, Claire, Pierre et toute l'équipe de Alain INARD qui s'est montrée, à chaque fois, intéressée et s'est impliquée dans tous nos développements et nos projets les plus fous. Finalement, le personnel de production et de support travaille toujours dans l'ombre mais effectue 90% de la fabrication de nos plaques, je ne les remercierai jamais assez. J'adresse en particulier mes remerciements à l'équipe de métrologie, Séverine, Délia, Laurent et Vincent, qui ont toujours été prêts à mesurer nos plaques et nous aider à y voir plus clair.

Les équipes de caractérisation jouent un grand rôle quand nous perdons un peu pied dans la complexité de nos structures. Je remercie ainsi l'équipe de caractérisation physique de Crolles, et également Fabienne SAGUIN à Crolles, et Cyril HAINAUT à Bordeaux, d'avoir su tirer le meilleur d'équipements de caractérisation électrique souvent capricieux.

Un petit merci particulier à Jessy BUSTOS, des modules avancés, pour les heures passées sur le layout de nos structures (à regarder des carrés).

J'adresse mes remerciements amicaux à toutes les personnes qui ont contribué à l'ambiance de franche camaraderie au cours de ces années à Crolles. Toutes les personnes du groupe des filières R&D (toujours dans l'ordre des box, toujours) : Dominik, André, Isa, Stéphanie, Germaine, Jocelyne, Bertrand Z. (pour le basket et... chut !), Laurence, Agustin, Seb J. (co-fondateur du box trip-hop et IT support), Simon (Lapin), Philippe, Seb C., Sylvie, les exilés : Bertrand M. et Jean-Christophe et nos supers assistantes Chrystèle et Laurie.

Merci aux thésards de l'IXL, Brice, Pierre-Yvan et tous les autres, pour les discussions et les pauses et surtout merci à Seb pour cette collaboration mémorable.

Bravo aux thésards de ST qui font vivre l'entreprise en croyant servir la science. En filière, notre glorieux ancêtre Carlo, les suivants Julien et Jean-Philippe, les jeunes Boris, Pierre-Marie, Gaëlle et Carine, le très jeune David. Dans les autres services, Florence, Gaël, Hélène, Nico L., Luc, Nico G, Marie et Hélène. Mes plus chaleureux remerciements vont à mes confrères et consœurs docteurs en filière de 2003 : Steph, Aurélie, Doro et Ben.

J'adresse toute ma reconnaissance aux personnes qui m'ont aidé, accompagné, soutenu, et que j'aurais pu oublier dans ces quelques lignes.

Je remercie enfin mes parents, sans qui je ne serai pas arrivé jusque là et qui se sont impliqués personnellement dans la correction orthographique de ce manuscrit, et ma chère épouse, Priscilla (ma plus grande fan, ma muse et ma tête) pour ses conseils avisés sur les présentations orales et ma tenue vestimentaire, mais surtout pour son soutien quotidien et indéfectible.

# Sommaire

| Sommaire                                                                                                     | 1                           |

|--------------------------------------------------------------------------------------------------------------|-----------------------------|

| Résumé                                                                                                       | 7                           |

| Abstract                                                                                                     | 8                           |

| Glossaire                                                                                                    | 9                           |

|                                                                                                              |                             |

| Introduction générale                                                                                        | 11                          |

| I. Le Transistor bipolaire à hétérojo                                                                        | nctions Si/SiGe15           |

| I.1. Introduction                                                                                            | 15                          |

|                                                                                                              |                             |

| I.2. Rappels sur le fonctionnement du                                                                        | <del>-</del>                |

| I.2.A. Fonctionnement statique                                                                               |                             |

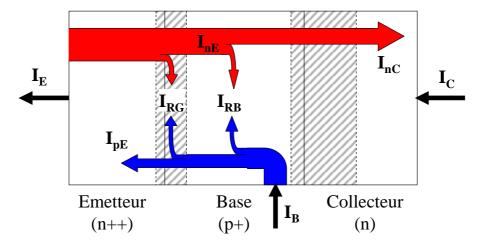

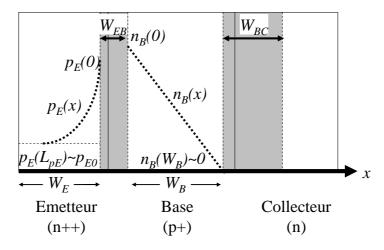

| I.2.A.1. Principe de fonctionnement                                                                          |                             |

|                                                                                                              |                             |

|                                                                                                              | <i>bipolaire15</i>          |

| I.2.A.2. Expressions des courants                                                                            | <u>17</u>                   |

|                                                                                                              |                             |

|                                                                                                              |                             |

| ~                                                                                                            |                             |

| I.2.B. Fonctionnement dynamique                                                                              |                             |

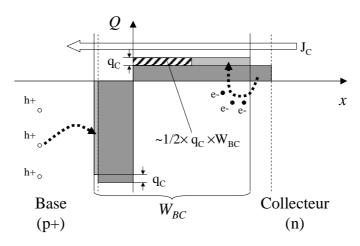

| I.2.B.1. Temps de transit $\tau_{\rm F}$                                                                     | 21                          |

| •                                                                                                            | 21                          |

| •                                                                                                            | 22                          |

|                                                                                                              | ollecteur: $\tau_{BC}$      |

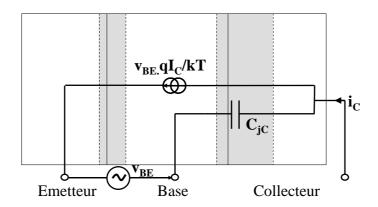

| I.2.B.2. <u>Fréquence de transition f<sub>T</sub></u> I.2.B.2.a. Expression du courant de collecteur         | i <sub>C</sub> 25           |

| 1.2.B.2.b. Expression du courant de base $i_B$                                                               | 25                          |

|                                                                                                              | 25<br>2f <sub>T</sub>       |

|                                                                                                              |                             |

| I.2.B.3. <u>Fréquence maximum d'oscillation f<sub>MAX</sub></u> I.2.C. Effets de forte polarisation et de fo | orte injection 28           |

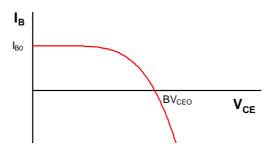

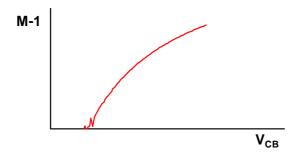

| I.2.C.1. Effets d'avalanche                                                                                  | 28 <u>28</u>                |

|                                                                                                              | 28                          |

|                                                                                                              | teur: $BV_{CEO}$            |

| I.2.C.2. Effet Early                                                                                         | 30                          |

| I.2.C.3. Effet Kirk                                                                                          | 31                          |

| I.2.C.4. Effet des résistances séries                                                                        | 32                          |

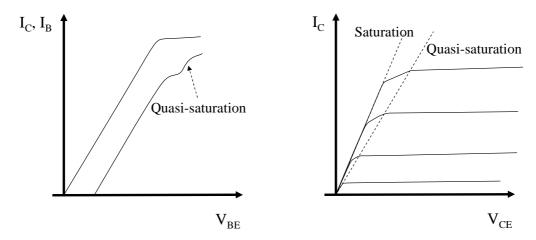

| I.2.D. Influence d'une base SiGe sur le f                                                                    | onctionnement du transistor |

| bipolaire                                                                                                    | 33                          |

|                                                                                                              | 33                          |

| I.2.D.2. <u>Impact sur les caractéristiques statiques</u>                                                    |                             |

| I.2.D.2.a. Gain en courant                                                                                   | 34                          |

|                                                                                                              | 35                          |

| I.2.D.3. <u>Influence sur les performances dynamiques</u>                                                    | 35                          |

| I.3. Caractérisation électrique                                                                              | 37                          |

| I.3.A. Courbes de Gummel et réseaux de                                                                       | e sortie37                  |

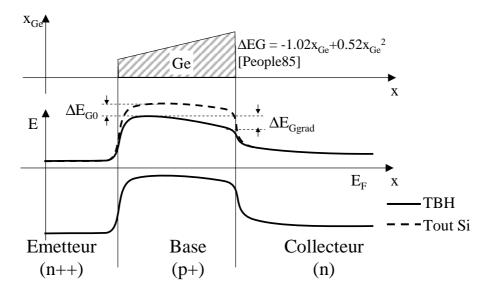

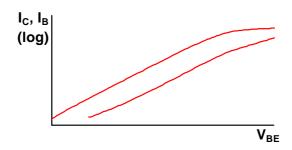

| I.3.A.1. Courbes de Gummel                                                                                   | 37                          |

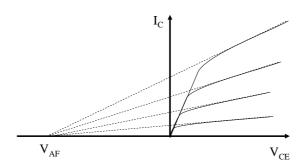

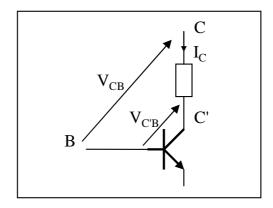

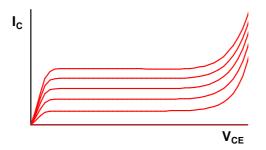

| I.3.A.2. Caractéristiques de sortie du transistor bipol                                                      |                             |

| I.3.B. Avalanche et auto-échauffement.                                                                       |                             |

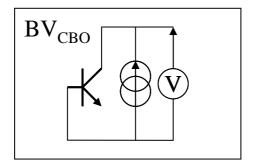

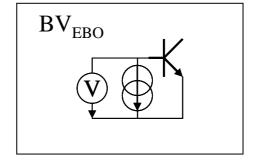

| I.3.B.1. Ter                      | nsions de claquage des jonctions : BV <sub>EBO</sub> , BV <sub>CBO</sub>        | 38       |

|-----------------------------------|---------------------------------------------------------------------------------|----------|

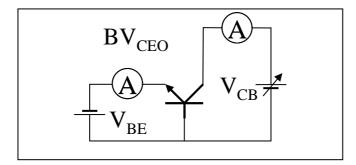

| I.3.B.2. Ter                      | nsion de claquage du dispositif en fonctionnement : BV <sub>CEO</sub>           | 39       |

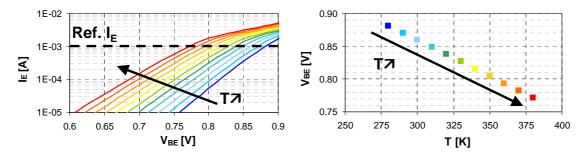

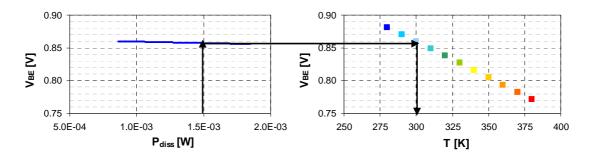

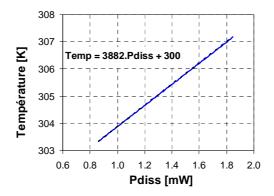

|                                   | sistance thermique                                                              | 40       |

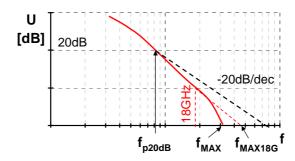

|                                   | uence de transition et fréquence maximale d'oscillation.                        | 12       |

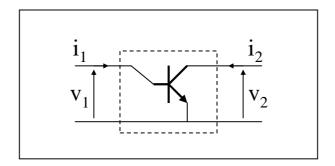

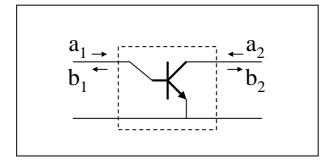

| I.3.C.1. The                      | éorie des quadripôles                                                           | 42       |

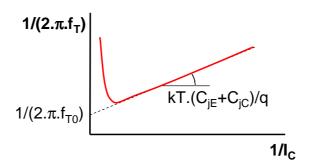

| I.3.C.2. Fré                      | éorie des quadripôles<br>quence de transition et temps de transit               | 44       |

| 1.3.C.2. <u>110</u><br>1.3.C.2.a. | $\frac{quence}{Fréquence}$ de transition $f_T$                                  |          |

| I.3.C.2.b.                        | Temps de transit $	au_F$                                                        |          |

|                                   | quence maximale d'oscillation f <sub>MAX</sub>                                  |          |

|                                   | <del></del>                                                                     |          |

|                                   |                                                                                 | 46       |

| <u> </u>                          | n d'un TBH Si/SiGe sur substrat SOI mince                                       |          |

| II.1. Introdu                     | action                                                                          | 47       |

| II.2. Etat de                     | e l'art du bipolaire sur SOI : vers le choix d'une intég                        | ration47 |

| II.2.A. Evol                      | ution des architectures existantes                                              | 47       |

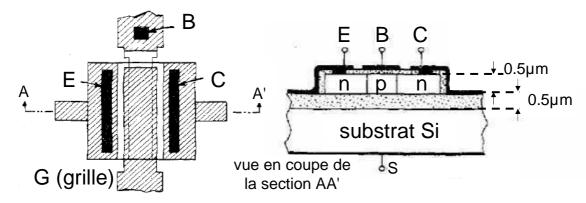

| II.2.A.1. Tra                     | nsistors bipolaires latéraux                                                    | 47       |

| II.2.A.1.a.                       | unsistors bipolaires latéraux  Premiers transistors bipolaires latéraux sur SOI | 48       |

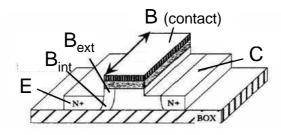

| II.2.A.1.b.                       |                                                                                 |          |

| II.2.A.1.c.                       |                                                                                 |          |

| II.2.A.2. <u>Tra</u>              | nsistors bipolaires verticaux sur SOI épais                                     |          |

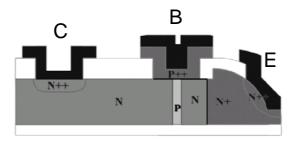

| II.2.A.3. <u>Tra</u>              | insistors bipolaires verticaux sur SOI mince                                    |          |

| II.2.A.3.a.                       |                                                                                 |          |

| II.2.A.3.b.                       | TT TTTT                                                                         |          |

|                                   | an des architectures présentées                                                 | 54       |

| II.2.B. Arch                      | itecture retenue pour cette étude                                               | 55       |

| II.2.B.1. Des                     | scription de la structure                                                       |          |

|                                   |                                                                                 | 58       |

|                                   | tions physiques pour la validation de l'intégration                             |          |

| II.3.A. Desc                      | ription de l'environnement de simulation et des paramèt                         | res 58   |

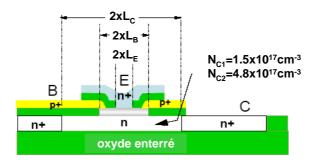

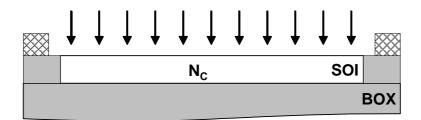

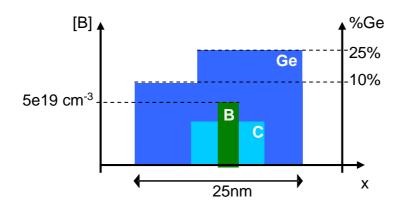

| II.3.A.1. <u>Des</u>              | scription de la structure simulée                                               | 58       |

| II.3.A.1.a.                       | Géométrie de la structure                                                       | 58       |

| II.3.A.1.b.                       | Caractéristiques des matériaux                                                  | 59       |

|                                   | amètres variables de l'étude                                                    |          |

| II.3.A.2.a.                       | 1 0                                                                             |          |

| II.3.A.2.b.                       | C                                                                               |          |

| II.3.A.3. <u>Sim</u>              | nulations physiques                                                             | 61       |

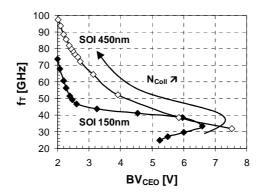

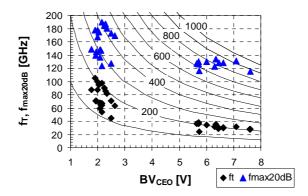

| II.3.B. Résu                      | ltats de simulations de f <sub>Tmax</sub> et BV <sub>CEO</sub>                  | 62       |

|                                   | luence de la concentration des dopants du collecteur                            |          |

| II.3.B.1.a.                       | Tension de claquage du transistor BV <sub>CEO</sub>                             | 62       |

| II.3.B.1.b.                       |                                                                                 |          |

| II.3.B.2. <u>Eff</u>              | ets de la distance de la prise de contact collecteur                            | 64       |

| II.4. Réalisa                     | tion et caractérisation des dispositifs                                         | 66       |

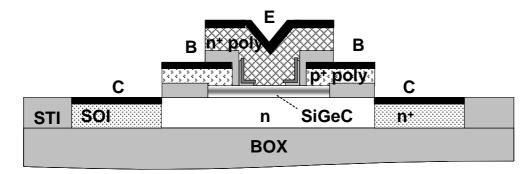

| II.4.A. Fabri                     | ication des échantillons                                                        | 66       |

| II.4.A.1. Org                     | ganisation de la fabrication                                                    | 66       |

| II.4.A.2. <u>Enc</u>              | chaînement des étapes de fabrication                                            | 67       |

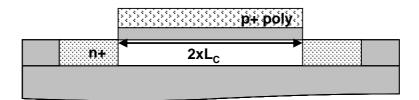

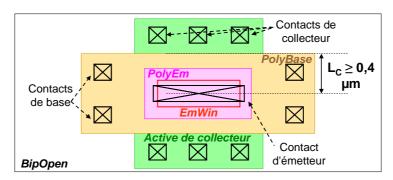

| II.4.A.2.a.                       | Zones actives et « BipOpen »                                                    | 67       |

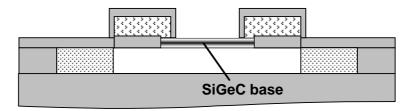

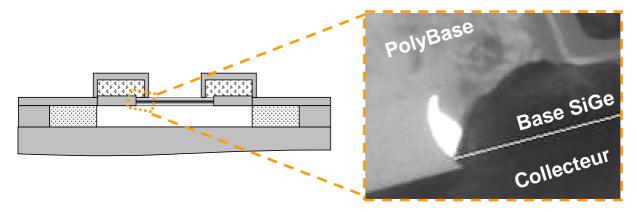

| II.4.A.2.b.                       | 1 · · · · · · · · · · · · · · · · · · ·                                         |          |

| II.4.A.2.c.                       | Fenêtre émetteur et dépôt de la base                                            |          |

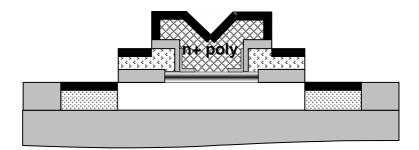

| II.4.A.2.d.                       | Emetteur et fin de la fabrication                                               | 70       |

| II.4.B. Conc                      | ception des dispositifs                                                         | 72       |

|                                   | lisation des masques et règles de dessin                                        |          |

| II.4.B.2. Opt                     |                                                                                 | =-       |

| II.4.B.2.a.                       |                                                                                 |          |

| II.4.B.2.b.                       | ů                                                                               |          |

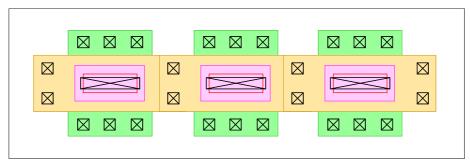

| II.4.B.2.c.                       | Le dessin cellulaire du transistor                                              | 75       |

| II.4.C. C                                                                                                                                                                                            | aractérisations des dispositifs                                                                                                                                                                                     | 76                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

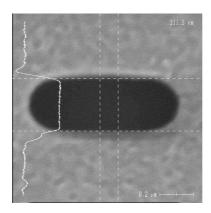

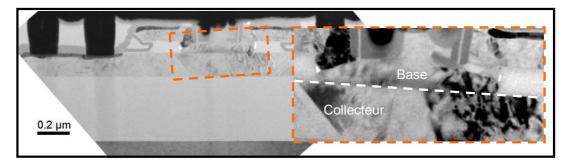

|                                                                                                                                                                                                      | <u>Caractérisation physique</u>                                                                                                                                                                                     |                                                   |

| II.4.C.                                                                                                                                                                                              |                                                                                                                                                                                                                     | 76                                                |

| II.4.C.                                                                                                                                                                                              |                                                                                                                                                                                                                     |                                                   |

| II.4.C.2.                                                                                                                                                                                            | Caractérisation électrique                                                                                                                                                                                          | 78                                                |

| II.4. C.                                                                                                                                                                                             |                                                                                                                                                                                                                     |                                                   |

| II.4.C.                                                                                                                                                                                              | 4                                                                                                                                                                                                                   |                                                   |

| II.4.C.                                                                                                                                                                                              | 2.c. Mesures hyperfréquence                                                                                                                                                                                         | 79                                                |

| II.5. Con                                                                                                                                                                                            | clusion                                                                                                                                                                                                             | 80                                                |

| III. Fonction                                                                                                                                                                                        | nnement du TBH Si/SiGe sur SOI mince                                                                                                                                                                                | 81                                                |

| III.1. Intr                                                                                                                                                                                          | oduction                                                                                                                                                                                                            | 81                                                |

| III.2. Ana                                                                                                                                                                                           | lyse du mécanisme d'avalanche par simulation physique                                                                                                                                                               | 2D81                                              |

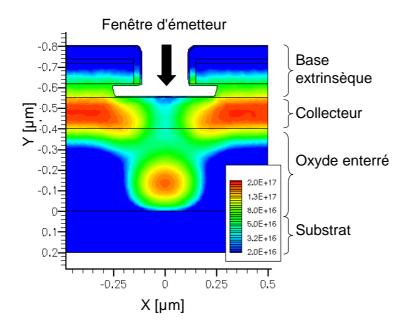

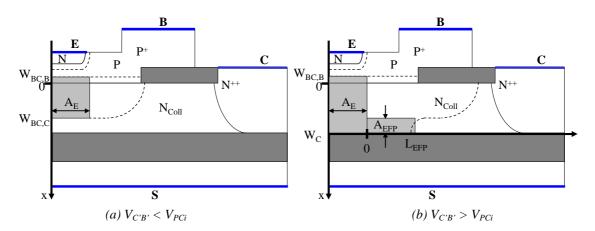

|                                                                                                                                                                                                      | nalyse de la localisation de la zone de désertion base-collect                                                                                                                                                      |                                                   |

|                                                                                                                                                                                                      | Description de la méthode                                                                                                                                                                                           | 0.1                                               |

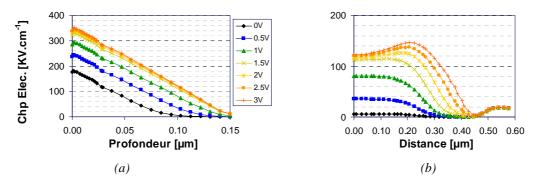

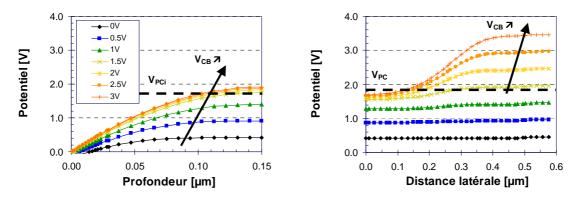

| III.2.A.2.                                                                                                                                                                                           | Evolution de la ZCE base-collecteur en fonction de la tension V <sub>CB</sub>                                                                                                                                       | 82                                                |

|                                                                                                                                                                                                      | tude du fonctionnement du dispositif                                                                                                                                                                                |                                                   |

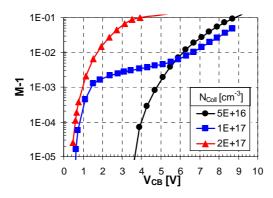

| III.2.D. E.                                                                                                                                                                                          | Dispositif typique dopé à 10 <sup>17</sup> cm <sup>3</sup>                                                                                                                                                          | 84                                                |

|                                                                                                                                                                                                      | Dispositif typique dopé à $10^{17}$ cm <sup>-3</sup><br>8.1.a. Analyse de la désertion verticale dans le collecteur : Saturation du facteur                                                                         | 01                                                |

|                                                                                                                                                                                                      | d'avalanche                                                                                                                                                                                                         |                                                   |

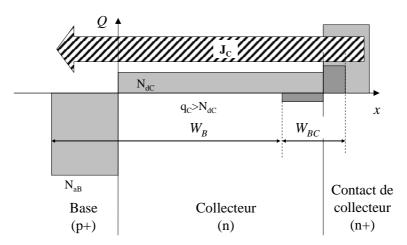

| III.2.E                                                                                                                                                                                              | 3.1.b. Analyse de la désertion totale du collecteur : Influence de la position de la                                                                                                                                | orise de                                          |

|                                                                                                                                                                                                      | collecteur                                                                                                                                                                                                          |                                                   |

|                                                                                                                                                                                                      | Influence du dopage collecteur sur l'extension de la zone de désertion                                                                                                                                              | 87                                                |

| III.2.E                                                                                                                                                                                              |                                                                                                                                                                                                                     |                                                   |

| III.2.E                                                                                                                                                                                              | ······································                                                                                                                                                                              |                                                   |

| III.2.C.C                                                                                                                                                                                            | onclusion sur l'avalanche dans le collecteur                                                                                                                                                                        | 89                                                |

|                                                                                                                                                                                                      |                                                                                                                                                                                                                     |                                                   |

|                                                                                                                                                                                                      | actérisation électrique et influence des caractéristiques                                                                                                                                                           |                                                   |

|                                                                                                                                                                                                      | actérisation électrique et influence des caractéristiques<br>nologiques du collecteur                                                                                                                               | 89                                                |

| tech                                                                                                                                                                                                 | nologiques du collecteur                                                                                                                                                                                            |                                                   |

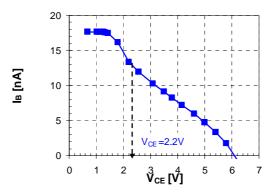

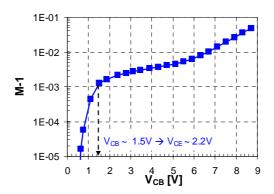

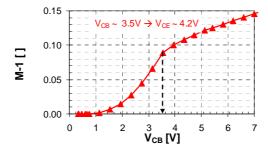

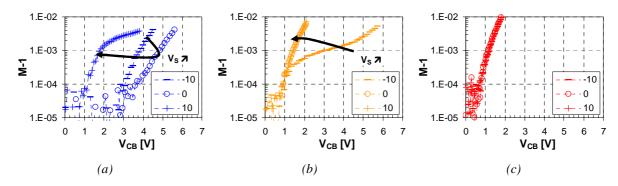

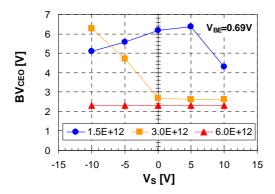

| tech<br>III.3.A.A                                                                                                                                                                                    | <b>nologiques du collecteur</b><br>valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                              | 89                                                |

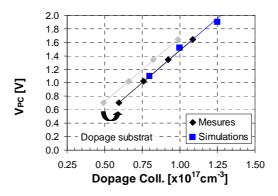

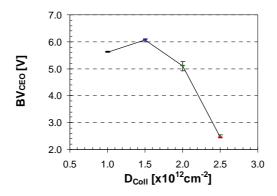

| tech<br>III.3.A.A                                                                                                                                                                                    | nologiques du collecteur  valanche dans le transistor réel et extraction du BV <sub>CEO</sub> Comparaison entre résultats de mesures et de simulations  1.1.a. Mesures sur lots en fonction du dopage de collecteur | 89<br>89                                          |

| tech<br>III.3.A.A<br>III.3.A.1.<br>III.3.A<br>III.3.A                                                                                                                                                | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89<br>89<br>89                                    |

| tech<br>III.3.A.A<br>III.3.A.1.<br>III.3.A<br>III.3.A                                                                                                                                                | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89<br>89<br>90                                    |

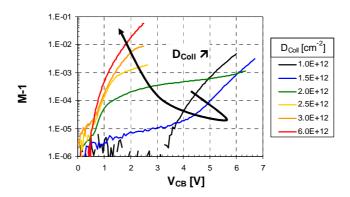

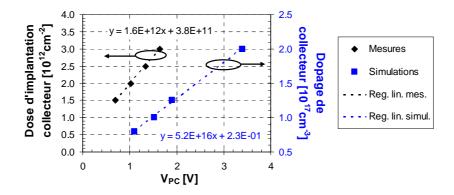

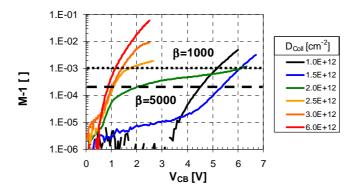

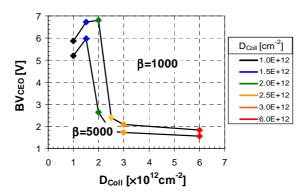

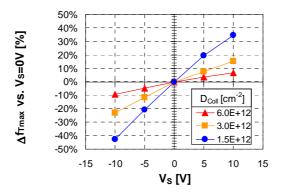

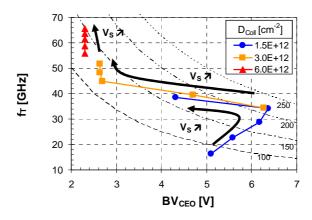

| tech<br>III.3.A.A<br>III.3.A.1.<br>III.3.A<br>III.3.A.2.<br>III.3.A.2.                                                                                                                               | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 898990 9292                                    |

| tech<br>III.3.A.A<br>III.3.A.1.<br>III.3.A<br>III.3.A.2.<br>III.3.A<br>III.3.A                                                                                                                       | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89<br>89<br>89<br>90<br>92<br>92                  |

| tech III.3.A.A III.3.A.1. III.3.A III.3.A III.3.A III.3.A.2. III.3.A III.3.A                                                                                                                         | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929294                                    |

| tech III.3.A.A III.3.A.1. III.3.A III.3.A III.3.A III.3.A.2. III.3.A III.3.A III.3.B.A                                                                                                               | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 92929495                                  |

| tech III.3.A.A III.3.A.1. III.3.A III.3.A III.3.A III.3.A.2. III.3.A III.3.B III.3.B.1. III.3.B.2.                                                                                                   | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96                                 |

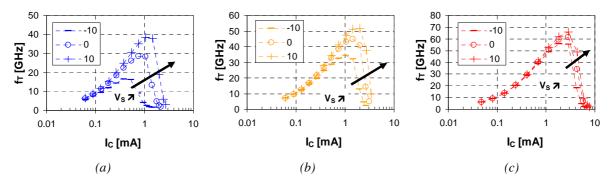

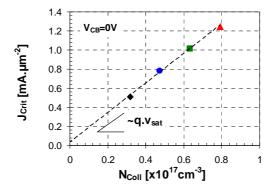

| tech III.3.A.A. III.3.A.1. III.3.A.2. III.3.A.2. III.3.A.3. III.3.B.A. III.3.B.1. III.3.B.1. III.3.C. In                                                                                             | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 92929495 96                               |

| tech III.3.A.A. III.3.A.1. III.3.A.2. III.3.A.2. III.3.A.3. III.3.B.A. III.3.B.1. III.3.B.2. III.3.C.1.                                                                                              | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 95 96                              |

| tech III.3.A.A III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.C.In III.3.C.1. III.3.C.2.                                                                                      | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98                              |

| tech III.3.A.A III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.2. III.3.C.2.                                                                           | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98 98                           |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A III.3.A III.3.A.2. III.3.A III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.2. III.3.C.3.                                                             | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 90  92 94 95  96  98  98  98  99 100           |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A III.3.A.2. III.3.A III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.1. III.3.C.2. III.3.C.3. III.3.C.3.                                               | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98 98 9899                      |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A III.3.A III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.1. III.3.C.2. III.3.C.3. III.3.C.3. III.4. Con               | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98 98 100 101                   |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.C.1. III.3.C.1. III.3.C.2. III.3.C.3. III.4. Con IV. Optimis                                         | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98 98 98 100 101 102105         |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.C.1. III.3.C.1. III.3.C.2. III.3.C.3. III.4. Con IV. Optimis                                         | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 89 8990 929495 96 98 98 98 100 101 102105      |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.1. III.3.C.3. III.4. Con IV. Optimis IV.1. Intr                              | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 89 8990 9295 96 98 98 98 100 101 102105        |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.1. III.3.B.2. III.3.C.1. III.3.C.2. III.3.C.3. III.4. Con IV. Optimis IV.1. Intr IV.2. Opt                              | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 89 8990 9295 96 98 98 98 98 100 101 102105     |

| tech III.3.A.A III.3.A.1. III.3.A.1. III.3.A.2. III.3.A.2. III.3.B.A III.3.B.A III.3.B.2. III.3.C.1. III.3.C.1. III.3.C.2. III.3.C.3. III.4. Con IV. Optimis IV.1. Intr IV.2. Opt IV.2.A.O IV.2.A.1. | valanche dans le transistor réel et extraction du BV <sub>CEO</sub>                                                                                                                                                 | 89 8990 929495 96 98 98 98 100 101 102105 105 106 |

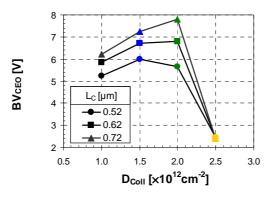

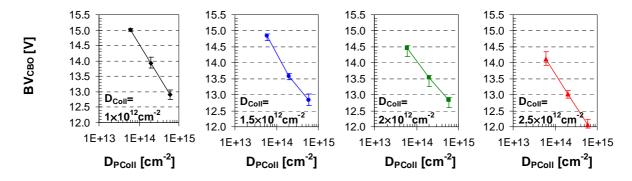

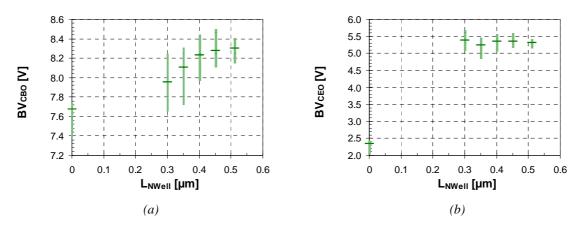

| IV.2.A.1.b. Tension de claquage BV <sub>CEO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

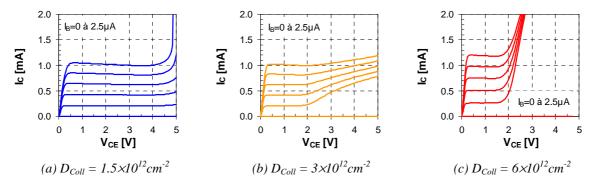

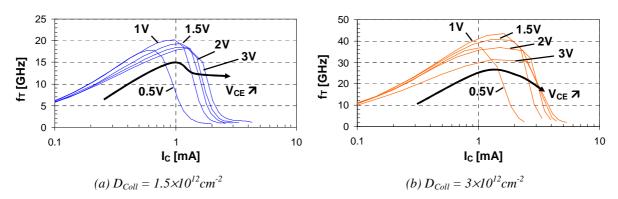

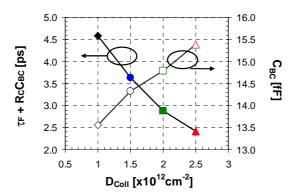

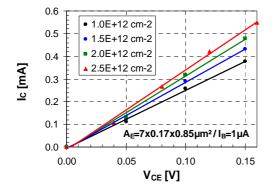

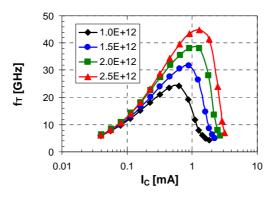

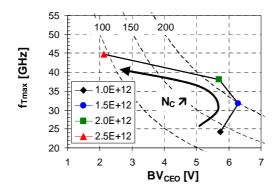

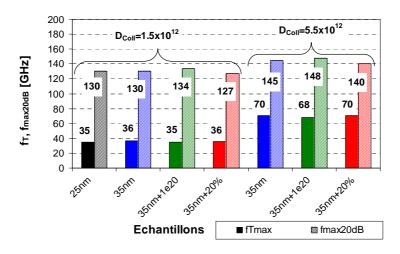

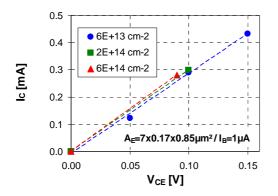

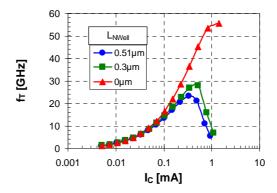

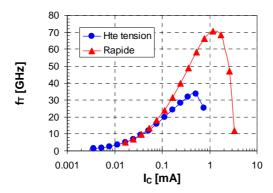

| IV.2.A.1.c. Caractéristiques dynamiques                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |

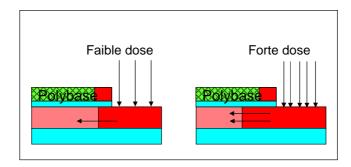

| IV.2.A.2. Profil de base                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |

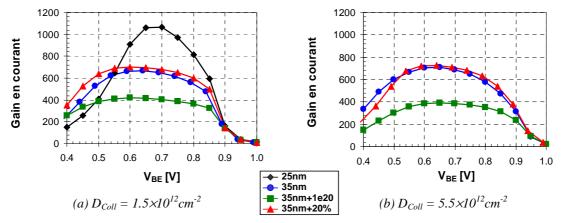

| IV.2.A.2.a. Effets sur le gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110                                    |

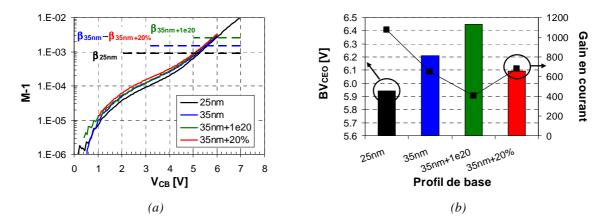

| IV.2.A.2.b. Facteur de multiplication et tension de claquage                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

| IV.2.A.2.c. Influence du profil de base sur la fréquence de transition                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

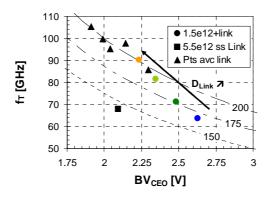

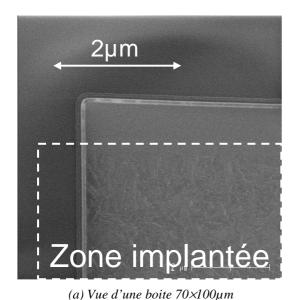

| IV.2.A.3. <u>Implantation sélective auto-alignée du collecteur extrinsèque : « le link »</u>                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

| IV.2.A.4. Surdopage de la prise de collecteur                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117                                    |

| IV.2.B.Optimisation du dessin des masques                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119                                    |

| IV.2.B.1. Fractionnement de l'émetteur                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| IV.2.B.1.a. Intérêt du fractionnement                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

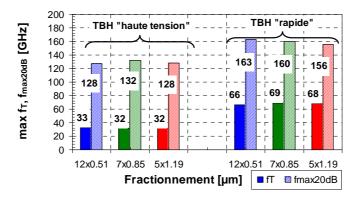

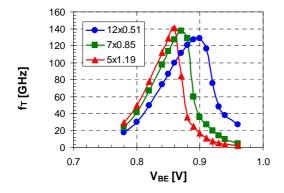

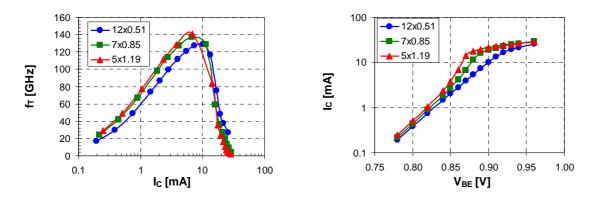

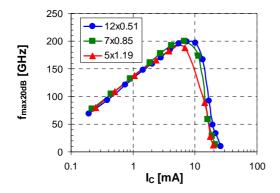

| IV.2.B.1.b. Impact du fractionnement sur les performances des dispositifs RF                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

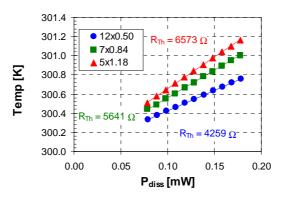

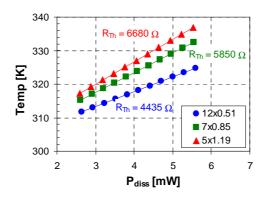

| IV.2.B.1.c. Résistance thermique et échauffement                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

| IV.2.B.2. Symétrie des structures                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 122                                    |

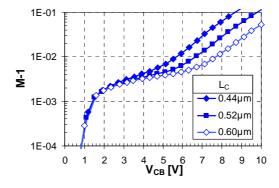

| IV.2.B.3. <u>Distance de la prise de collecteur</u>                                                                                                                                                                                                                                                                                                                                                                                                                                            | 123                                    |

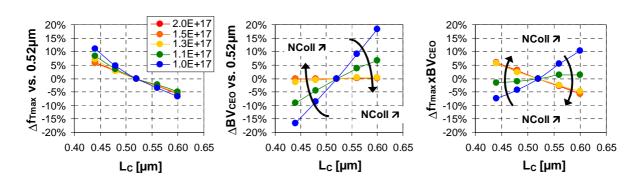

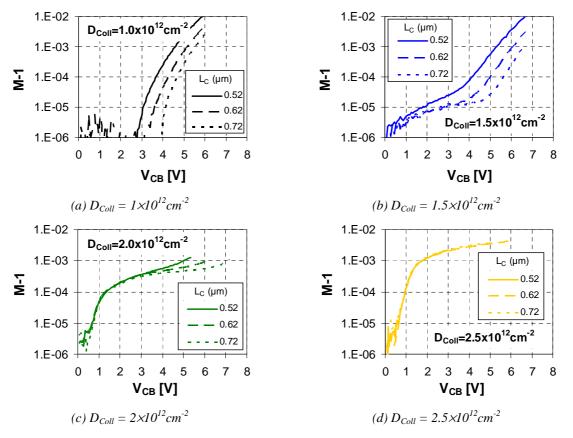

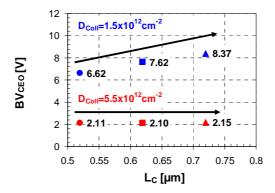

| IV.2.B.3.a. Influence sur la tension de claquage des dispositifs                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

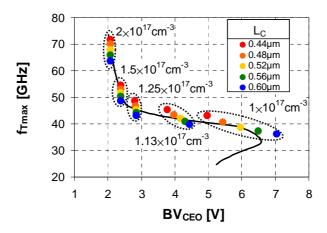

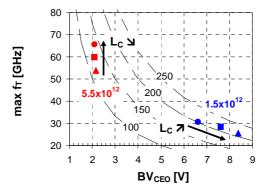

| IV.2.B.3.b. Amélioration des performances du transistor par variation de $L_C$                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

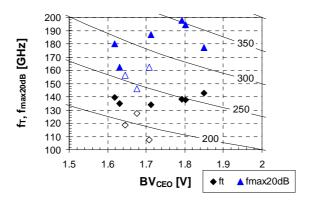

| IV.2.B.4. Conclusion sur l'optimisation des TBH sur SOI pour applications RF                                                                                                                                                                                                                                                                                                                                                                                                                   | 126                                    |

| IV.3. Optimisation du TBH sur SOI mince pour les très haute                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                      |

| fréquences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 127                                    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| IV.3.A.Optimisation du procédé de fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

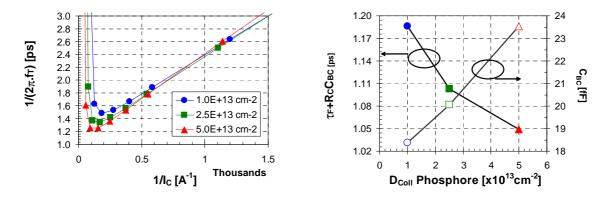

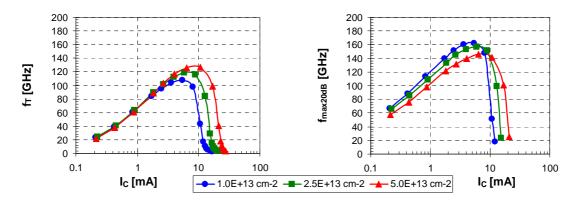

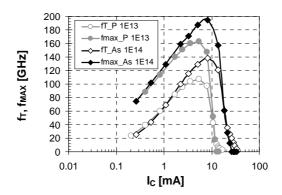

| IV.3.A.1. Collecteur implanté phosphore                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |

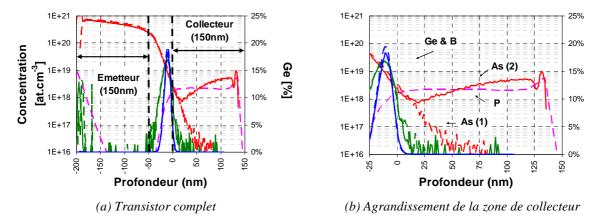

| IV.3.A.2. <u>Implantation du collecteur avec de l'arsenic</u>                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

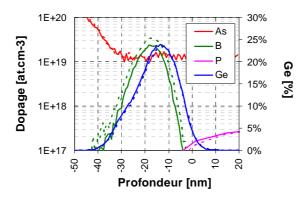

| IV.3.A.2.a. Profil d'implantation et implications                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| IV.3.B.Optimisation du dessin des masques                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| IV.3.B.1. Fragmentation de l'émetteur                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 133                                    |

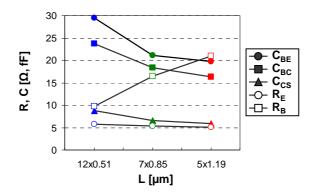

| IV.3.B.1.a. Résistances et capacités extraites des mesures dynamiques                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

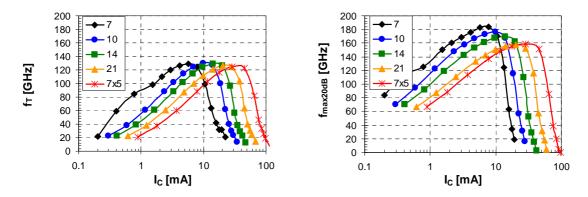

| IV.3.B.2. Nombre de cellules                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 136                                    |

| IV.3.B.3. Conclusion sur l'optimisation des transistors « très haute vitesse »                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| IV.4. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 138                                    |

| Dávolonnoment d'une technologie BiCMOS sur SOI r                                                                                                                                                                                                                                                                                                                                                                                                                                               | ninga 141                              |

| . Développement d'une technologie BiCMOS sur SOI r                                                                                                                                                                                                                                                                                                                                                                                                                                             | IIIICE 141                             |

| V.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 141                                    |

| V2 Décelement d'un modèle compet                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.41                                   |

| V.2. Développement d'un modèle compact                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 141                                    |

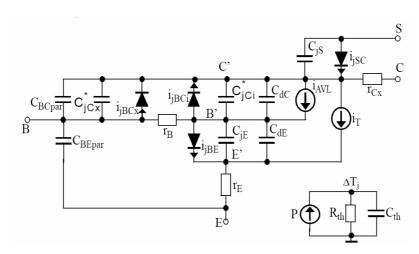

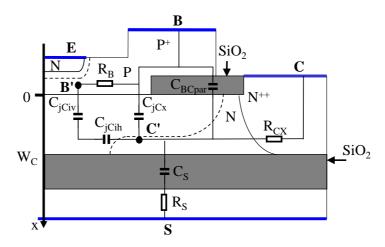

| V.2.A. Topologie du modèle adapté au SOI mince                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 141                                    |

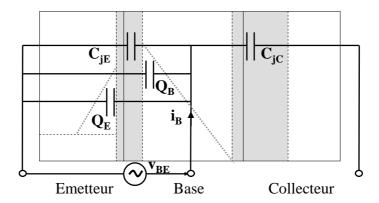

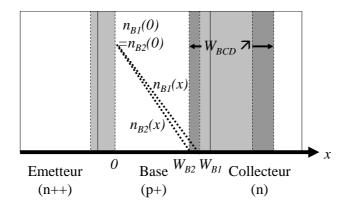

| V.2.A.1. Topologie de HICUM Level0 avant modifications                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| V.2.A.2. <u>Modifications de la topologie du modèle</u>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 143                                    |

| V.2.A.2.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 143                                    |

| V.2.A.2.b. Capacité collecteur-substrat                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 143                                    |

| V.2.A.2.c. Topologie du modèle HICUM du TBH sur SOI mince                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.4.4                                  |

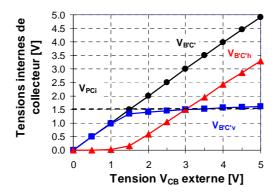

| V.2.A.3. <u>Définitions des tensions internes du modèle</u>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 144                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 144                                    |

| V.2.B. Equations du modèle                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 144<br>146                             |

| V.2.B.1. Valeurs des capacités et paramètres du modèle                                                                                                                                                                                                                                                                                                                                                                                                                                         | 144<br>146                             |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                    | 144<br>146<br>146<br>146               |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur  V.2.B.1.b. Paramètres du modèle                                                                                                                                                                                                                                                                                                                                                                   | 144<br>146<br>146<br>147               |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                    | 144<br>146<br>146<br>146<br>147        |

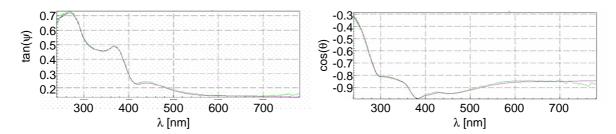

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                    | 144<br>146<br>146<br>147<br>147<br>147 |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                    | 144146146147147147                     |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur                                                                                                                                                                                                                                                                                                                                                                                                    | 144146146147147148148                  |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur  V.2.B.1.b. Paramètres du modèle  V.2.B.2. Définition des grandeurs relatives  V.2.B.2.a. Normalisation de l'inverse de la capacité de collecteur  V.2.B.2.b. Champ électrique dans la jonction base-collecteur  V.2.B.3. Equation du courant i <sub>T</sub> et influence de la nouvelle topologie  V.2.B.4. Equations du temps de transit                                                         | 144146146147147148148149               |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur  V.2.B.1.b. Paramètres du modèle  V.2.B.2. Définition des grandeurs relatives  V.2.B.2.a. Normalisation de l'inverse de la capacité de collecteur  V.2.B.2.b. Champ électrique dans la jonction base-collecteur  V.2.B.3. Equation du courant i <sub>T</sub> et influence de la nouvelle topologie  V.2.B.4. Equations du temps de transit  V.2.B.4.a. Composante de dérive-diffusion dans la base | 144146146147147148149                  |

| V.2.B.1. Valeurs des capacités et paramètres du modèle  V.2.B.1.a. Capacité base-collecteur  V.2.B.1.b. Paramètres du modèle  V.2.B.2. Définition des grandeurs relatives  V.2.B.2.a. Normalisation de l'inverse de la capacité de collecteur  V.2.B.2.b. Champ électrique dans la jonction base-collecteur  V.2.B.3. Equation du courant i <sub>T</sub> et influence de la nouvelle topologie  V.2.B.4. Equations du temps de transit                                                         | 144146146147147148149150               |

| V.2.B.4.d. Equation finale                                                                 | 152             |

|--------------------------------------------------------------------------------------------|-----------------|

| V.2.C. Comparaison du modèle avec des résultats de simulation                              |                 |

| et des mesures expérimentales                                                              |                 |

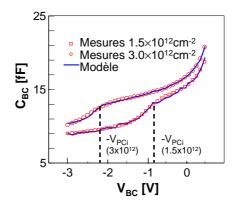

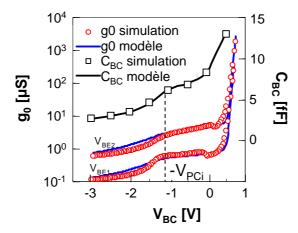

| V.2.C.1. Capacité base-collecteur                                                          |                 |

| V.2.C.2. Courant de collecteur                                                             | 154             |

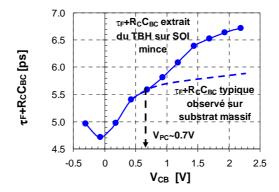

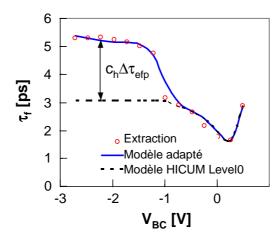

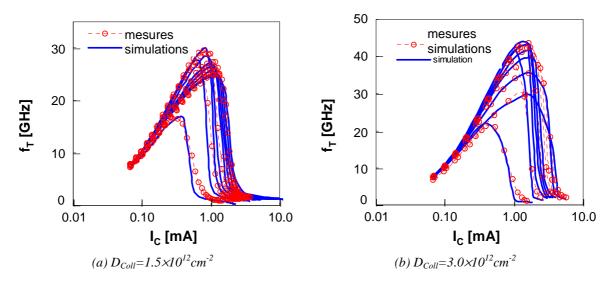

| V.2.C.3. Temps de transit et fréquence de transition                                       | 154             |

| V.3. Intégration dans une technologie BiCMOS                                               | 156             |

| V.3.A. Intégration commune des transistors MOS et bipolaires                               | 156             |

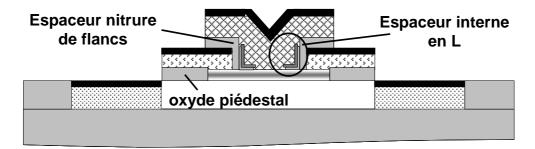

| V.3.A.1. Réduction de la hauteur du TBH                                                    | 157             |

| V.3.A.2. Espaceurs en D                                                                    | 158             |

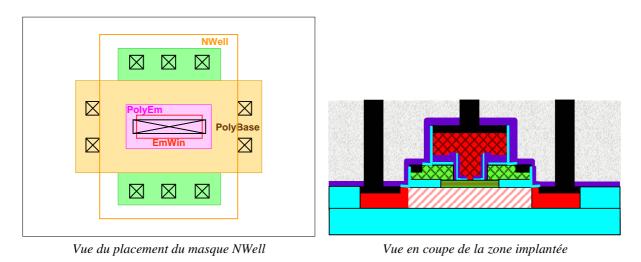

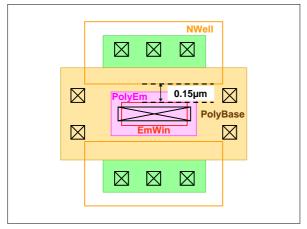

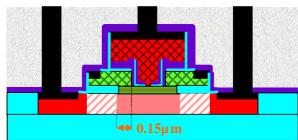

| V.3.A.3. <u>Utilisation du masque NWell dans le dessin des masques du transistor bipol</u> | aire 159        |

| V.3.A.3.a. Utilisation du masque NWell en complément du dopage de collecteur               | r159            |

| V.3.A.3.b. Utilisation du NWell pour l'implantation du collecteur extrinsèque              | 160             |

| V.3.A.3.c. Résultats électriques                                                           |                 |

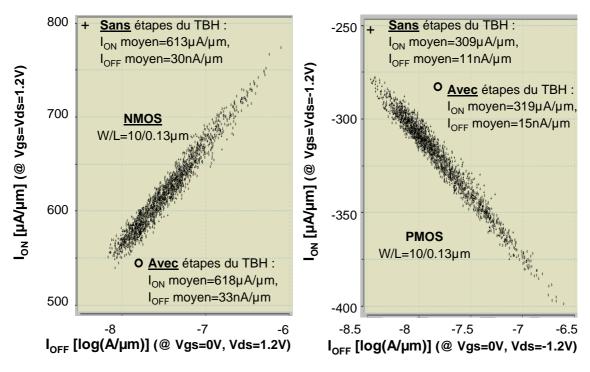

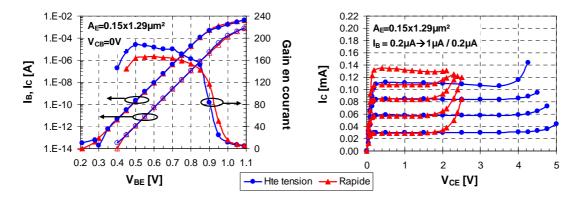

| V.3.A.4. Bilan du développement de la technologie BiCMOS SiGe sur SOI mince [B             | oissonnet06]163 |

| V.3.B. Etude du bruit à basses fréquences et de la fiabilité                               | 166             |

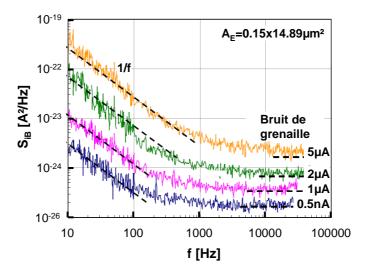

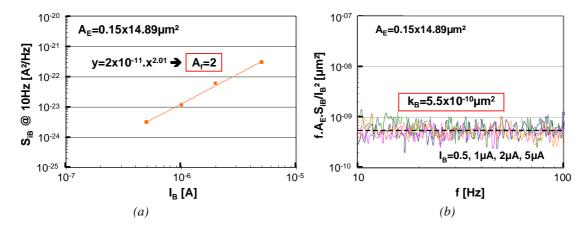

| V.3.B.1. Bruit basse fréquence                                                             | 166             |

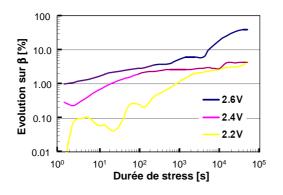

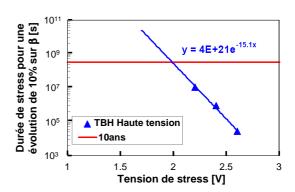

| V.3.B.2. Etude de fiabilité                                                                | 167             |

| V.4. Conclusion                                                                            | 168             |

| Conclusion générale                                                                        | 171             |

| Références bibliographiques                                                                | 175             |

| Liste des publications                                                                     | 178             |

## Résumé

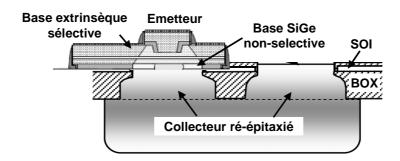

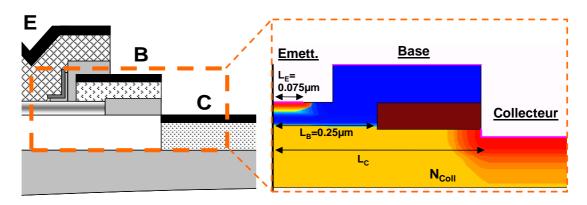

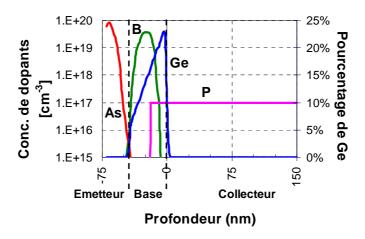

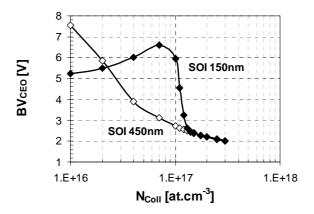

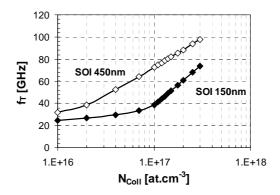

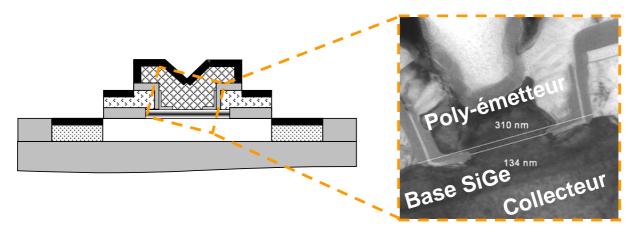

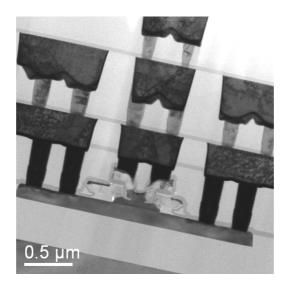

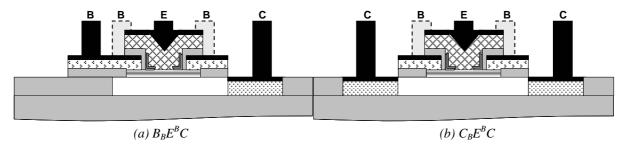

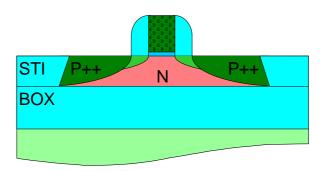

Pour les besoins des applications RF performantes, il semble nécessaire de développer un transistor bipolaire NPN en complément des technologies CMOS sur substrat SOI mince. Les spécifications envisagées pour un tel dispositif nous imposent l'utilisation d'une architecture verticale à hétérojonctions Si/SiGe dont le concept a été développé par IBM mais dont la réalisation reste expérimentale.

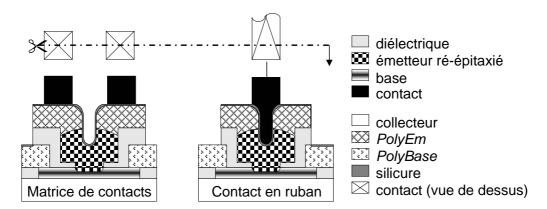

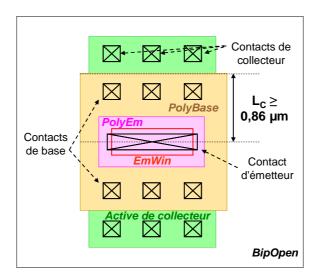

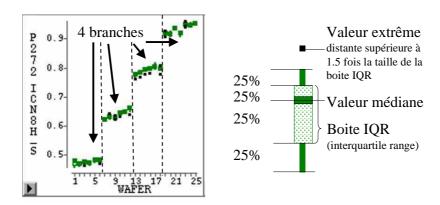

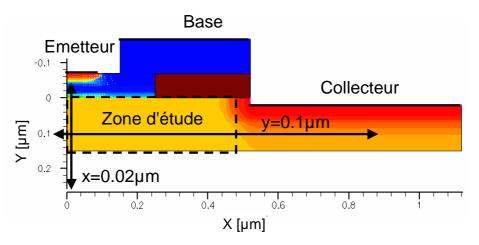

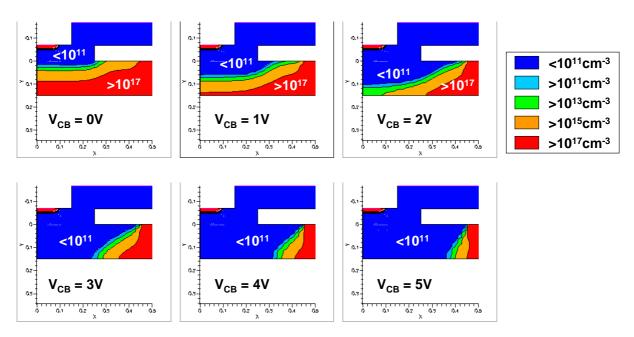

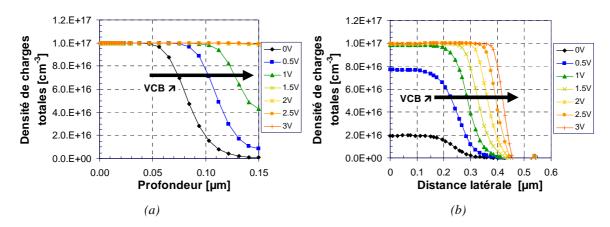

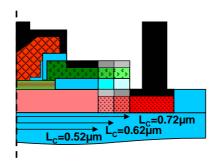

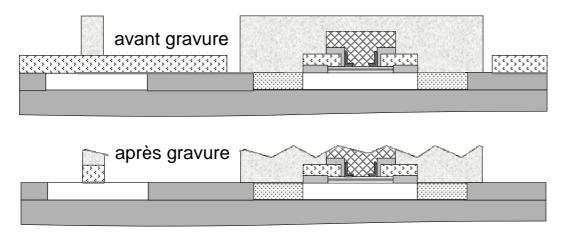

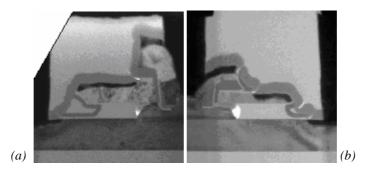

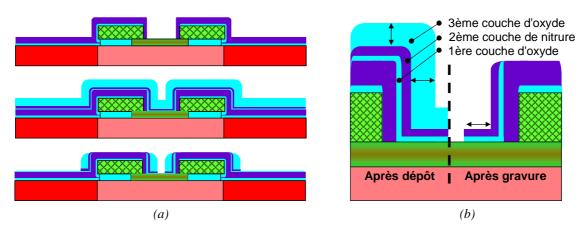

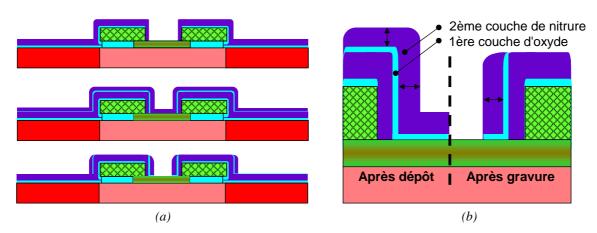

Nous proposons donc une nouvelle structure adaptée du concept de collecteur localisé dans la couche supérieure du SOI mais dont la structure émetteur-base s'inspire de l'architecture auto-alignée développée par STMicroelectronics. L'intégration présentée bénéficie de l'innovation apportée par le collecteur implanté et de la robustesse d'une structure émetteur-base industrielle. La structure complète peut être incorporée dans une technologie  $0.13\mu m$  sur SOI 150nm.